# Systems Engineering Laboratories

APR 4.1968

SEL 810A General Purpose Computer

| Why the SEL 810A?                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------|

| One Pass ASA FORTRAN IV with Complete<br>Sub-routine Library                                                                 |

| All Silicon Monolithic Integrated Circuits                                                                                   |

| 16-bit Binary Word Length Plus Parity and<br>Program Protect Bits                                                            |

| Up to 32,768 Words of Memory                                                                                                 |

| 1.75 Microsecond Full Cycle Time                                                                                             |

| Hardware Index Register Standard                                                                                             |

| Multi-Level Indirect Addressing                                                                                              |

| Fully Parallel Operation                                                                                                     |

| Extensive and Versatile Instruction List                                                                                     |

| Up to 96 Levels of Priority Interrupt                                                                                        |

| Communication over 64 Word Parallel Direct<br>Information Channels and up to eight automatic<br>Block Transfer Control Units |

| Complete Line of Peripheral Devices                                                                                          |

| Compatible with Systems Engineering<br>Laboratories Acquisition and Process Control<br>Sub-systems                           |

### Introduction

The SEL 810A is a 16-bit parallel digital computer using highly reliable silicon monolithic integrated circuits throughout. Offered with the basic computer is the most complete, powerful, field proven software package for a computer in its size or price class. SEL 810A programming is simplified by a powerful repertoire of direct address and augmented instructions.

The high degree of flexibility designed into the SEL 810A Computer and its enviable field reputation for reliability and performance, has made it the first choice of a large and rapidly growing list of customers with requirements running the full gambit of industrial and scientific real-time applications.

# **Computer Organization**

Basic SEL 810A hardware features include full cycle time of 1.75 microseconds with a minimum available core storage of 4096 words. Indexing and multi-level indirect addressing are additional basic features. Indexing operations require no additional time and both pre-indexing and post-indexing operations can be performed.

Additional basic computer features are hardware multiply and divide, hardware program counter, double precision accumulator, two priority interrupt levels, manual program stop, sixteen sense switches, hardware index register, real-time input/output system, power fail safe and a complete software package.

Standard options include additional core storage up to 32,768 words in 4k or 8k modules, up to 96 levels of individually armable priority interrupts. memory and input/output parity generator/checkers, up to eight automatic Block Transfer Control units and time sharing options including program protect, instruction trap, variable base register and stall alarm. The variable base register option permits separately assembled or compiled programs to be independently loaded into memory. The stall alarm option automatically restarts the computer should a stall condition occur. Additional standard options include auto start which restarts program execution when power is reapplied after a power failure, input/output typewriter, table top operator console, real-time clock and RFI treatment for the computer cabinet.

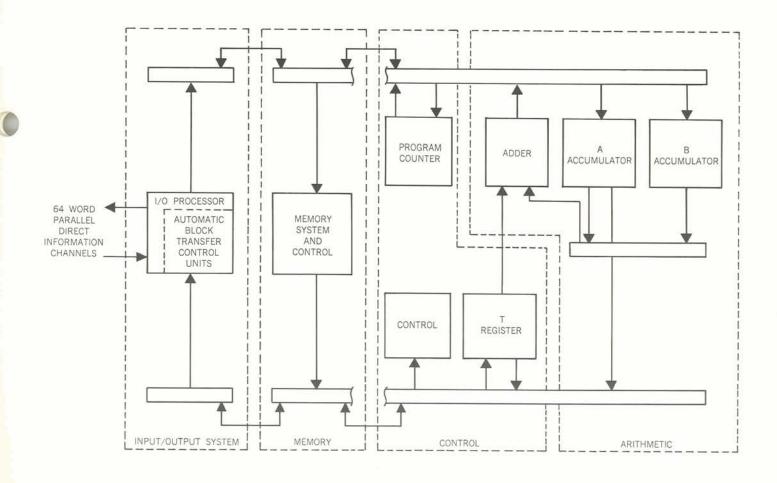

The basic input/output system of the SEL 810A permits program controlled single word transfers to and from any peripheral unit and memory or the A-Accumulator. Optional automatic Block Transfer Control units permit automatic transfers of up to 32,767 16-bit words to and from peripheral devices. These transfers are made over word parallel direct information channels on a priority request basis. Up to eight automatic Block Transfer Control units can be used at once. All units honor memory protect status and include all required hardware registers, automatic initialization and automatic reinitialization.

# **Physical Description**

The SEL 810A computer cabinet opens from the rear to provide access for servicing. Circuit modules are mounted on "pages" which swing out for service access. Wire wrap techniques are used exclusively to assure highest reliability.

## **Functional Description**

The input/output system of the SEL 810A contains the input/output processor and optional automatic Block Transfer Control units. Memory can consist of up to 32,768 16-bit words of core storage. The control section of the central processing unit includes a 15-bit program counter and a transfer register (T-Register) that stores all words from memory, pending operation. The arithmetic section of the central processing unit contains the upper arithmetic register (A-Accumulator), lower arithmetic register (B-Accumulator) that also serves as an index register, and a 16-bit parallel adder.

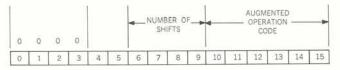

# Basic SEL 810A Word Formats

Four basic SEL 810A word formats are outlined in the following diagram:

INDIRECT ADDRESS FORMAT

DATA FORMAT

| S | 14<br>2 | 13<br>2 | 12<br>2 | 11<br>2 | 10<br>2 | 9<br>2 | 8<br>2 | 7<br>2 | 6<br>2 | 5  | 4  | 3<br>2 | 2  | 1<br>2 | 0<br>2 |

|---|---------|---------|---------|---------|---------|--------|--------|--------|--------|----|----|--------|----|--------|--------|

| 0 | 1       | 2       | 3       | 4       | 5       | 6      | 7      | 8      | 9      | 10 | 11 | 12     | 13 | 14     | 15     |

# Basic Computer

## Instruction List

The SEL 810A is equipped with a powerful repertoire of direct address and augmented instructions. This repertoire, including two 3-way INSTRUCTION FORMAT INDIRECT OPERATION CODE OPERAND ADDRESS INDEX MAP 11 12 13 14 15 0 1 2 4 5 6 8 9 10

AUGMENTED INSTRUCTION FORMAT

branch/skip instructions is coupled with hardware indexing and indirect address chaining, resulting in maximum program speed and flexibility. Indexing requires no additional instruction time. Indirect operations require an additional 1.75 microseconds per indirect level.

| CLASS       | CLASS CODE TIME FUNCTION<br>MNEMONIC (Microseconds) |       | FUNCTION                     | CLASS    | CODE<br>MNEMONIC | TIME<br>(Microseconds) | FUNCTION                                                                                                       |  |

|-------------|-----------------------------------------------------|-------|------------------------------|----------|------------------|------------------------|----------------------------------------------------------------------------------------------------------------|--|

| ARITHMETIC  | AMA                                                 | 3.5   | Add Memory to A              |          |                  |                        |                                                                                                                |  |

|             | AMB                                                 | 3.5   | Add Memory to B              | REGISTER | CLA'             | 1.75                   | Clear A                                                                                                        |  |

|             | SMA                                                 | 3.5   | Subtract Memory from A       | CHANGE   | TAB'             | 1.75                   | Transfer A to B                                                                                                |  |

|             | MPY                                                 | 7.0   | Multiply B times Memory      | 171      | IAB'             | 1.75                   | Interchange A and B                                                                                            |  |

|             | DIV                                                 | 10.5  | Divide A and B by Memory     |          | CSB'             | 1.75                   | Transfer B Sign to Carry                                                                                       |  |

|             | RNA'                                                | 1.75  | Round A by MSB in B          |          |                  |                        | and Clear B to Positive                                                                                        |  |

|             |                                                     | 00000 |                              |          | TBA'             | 1.75                   | Transfer B Sign to A                                                                                           |  |

| OAD/STORE   | LAA                                                 | 3.5   | Load A from Memory           |          |                  |                        |                                                                                                                |  |

| UND/ STONE  | LBA                                                 | 3.5   | Load B from Memory           | SHIFT    | RSA'             | Time for               | Right Shift A                                                                                                  |  |

|             | STA                                                 | 3.5   | Store Memory from A          | 14       | LSA'             | shifts varies          | Left Shift A                                                                                                   |  |

|             | STB                                                 | 3.5   | Store Memory from B          |          | FRA'             | as follows:            | Right Shift A and B                                                                                            |  |

|             | LCS                                                 | 1.75  | Load Control Switches in A   |          | FLA'             | Shifts Time            | Left Shift A and B                                                                                             |  |

|             | 163                                                 | 1.75  |                              |          | RSL <sup>4</sup> | 1-4 3.5                | Right Logical Shift A                                                                                          |  |

| RANCH/SKIP  | BRU                                                 | 1.75  | Unconditional Branch         |          | FRL'             | 5-8 5.25               | Logical Rotate A and B                                                                                         |  |

| BRANCH/SKIP | SPB                                                 | 3.5   | Store Place and Branch       |          |                  | 9-12 7.0               | Left                                                                                                           |  |

|             | SNS'                                                | 1.75  | Skip if Sense Switch Not Set |          | LSL!             | 13-15 8.75             | Left Logical Shift A                                                                                           |  |

|             | IMS                                                 | 5.25  | Increment Memory and Skip    |          | FLL'             | 10 10 0.70             | Left Logical Shift A and B                                                                                     |  |

|             | CMA                                                 | 5.25  | Compare Memory and A         |          |                  |                        |                                                                                                                |  |

|             | CIVIA                                               | 0.20  | (3 wav)                      | CONTROL  | HLT/             | 1.75                   | Halt                                                                                                           |  |

|             |                                                     |       | n+1(-), n+2(0), n+3(+)       | oon not  | NOP              | 1.75                   | No Operation                                                                                                   |  |

|             | IBS'                                                | 1.75  | Increment B (Index) and Skip | 1.5      | TOP              | 1.75                   | Turn off Interrupt                                                                                             |  |

|             | SAZ'                                                | 1.75  | Skip if A is Zero            |          | PIE'             | 3.5                    | Priority Interrupt Enable                                                                                      |  |

|             | SAP'                                                | 1.75  | Skip if A is Positive        |          | PID              | 3.5                    | Priority Interrupt Disable                                                                                     |  |

|             | SAN'                                                | 1.75  | Skip if A is Negative        |          | 1 10             | 0.0                    | the second s |  |

|             | SOF'                                                | 1.75  | Skip no Overflow             | INPUT/   | AIP              | 5.25                   | Accumulator Input                                                                                              |  |

|             | SAS                                                 | 1.75  | Skip on A. Sign (3 way)      | OUTPUT   | AOP              | 5.25                   | Accumulator Output                                                                                             |  |

|             | 343                                                 | 1.7.5 | n+1(-), n+2(0), n+3(+)       | 001101   | MIP              | 5.25                   | Memory Input                                                                                                   |  |

|             | SNO'                                                | 1.75  | Skip if A is Not Normalized  |          | MOP              | 5.25                   | Memory Output                                                                                                  |  |

|             | LOB                                                 | 3.5   | Long Branch                  |          | CEU              | 5.25                   | Command External Unit                                                                                          |  |

|             | LUB                                                 | 5.5   | Long Dranch                  |          | TEU              | 5.25                   | Test External Unit                                                                                             |  |

| OGICAL      | ABA'                                                | 1.75  | AND A and B                  |          | 120              | 0.20                   | for enternal onit                                                                                              |  |

| UGICAL      | OBA'                                                | 1.75  | OR A and B                   |          | PON*             | 3.5                    | Protect Bit ON                                                                                                 |  |

|             | NEG'                                                | 1.75  | Negate A                     |          | POF*             | 3.5                    | Protect Bit OFF                                                                                                |  |

|             |                                                     | 1.75  | Complement A sign            |          | TBV*             | 1.75                   | Transfer B to VBR                                                                                              |  |

|             | ASC'<br>CNS'                                        | 1.75  | Convert Number System        |          | TVB*             | 1.75                   | Transfer VBR to B                                                                                              |  |

\* Optional ' Augmented

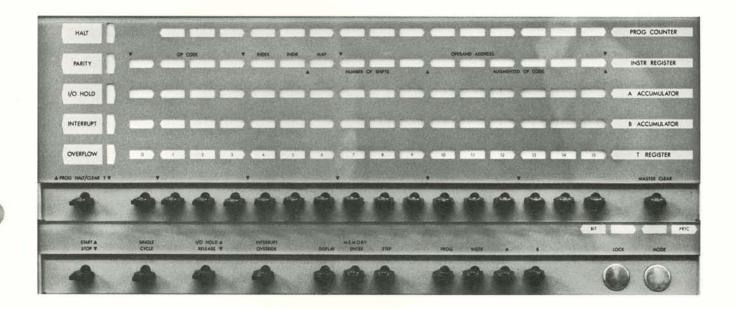

# **Operator Control Panels**

The SEL 810A has the most complete and functional control panel of any computer in its class. The entire control panel is designed for maximum operator/machine communication. Control panel functions include:

| Manual data entry from 16 data switches into T-Register                                                                                 | Manual Load and Display of memory locations                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manual transfer of T-Register contents to the<br>B-Accumulator, A-Accumulator, Instruction                                              | Manual Input/Output Hold/Release                                                                                                                        |

| Register and Program Counter<br>Manual program Start/Stop<br>Manual clear of individual registers plus Master<br>Clear of all registers | <ul> <li>Program protect bit indicator</li> <li>Key lock inhibit of all control switches*</li> <li>Key lock switch for program protect mode*</li> </ul> |

| Single Cycle control switch for manual program<br>advance                                                                               |                                                                                                                                                         |

\* Optional

# **SEL 810A**

### Programming Support

Standard and custom SEL 810A software packages have been delivered and are in use on a wide range of applications. Standard software packages include a Mnemonic Assembler (MNEMBLER), full USASI (United States of America Standards Institute) FORTRAN IV, Sub-routine Library, Utility Routines and Diagnostic Programs. All software packages are completely modular, permitting the addition of more powerful software elements as the basic configuration and size of the computer expands.

MNEMBLER—The SEL 810A Mnemonic Assembler translates programs written in symbolic code into meaningful machine language code. Designed to operate in the minimum computer configuration, MNEMBLER makes use of all available memory and all standard peripheral equipment. MNEMBLER operates in either a one-pass or two-pass mode. The one-pass mode offers significant time advantages at assembly time, while the two-pass mode results in a shorter object tape, more complete listings and error messages. All computer instructions are accepted by MNEMBLER. Thirteen special pseudo-operations are available for use by the programmer. FORTRAN IV — SEL 810A FORTRAN IV meets all USASI<sup>1</sup> standards and includes all the features and capabilities of FORTRAN II. Convenience features include one-pass operation, no reserved identifiers, mixed mode expressions, optional in-line assembly, tracing, mapping and chaining.

SUB-ROUTINE LIBRARY — The FORTRAN IV set is included and callable by both the FORTRAN IV compiler and MNEMBLER. Sub-routines in the package include Single and Double Precision Floating Point, Integer, Input/Output and control functions.

UTILITY ROUTINES — A large number of available Utility Routines include an efficient tape editor, on-line debug, dumps, trace, listing, conversion programs and input/output handlers.

<sup>1</sup>As suggested by American Standards Association, Section Committee X3, Computers and Information Processing.

DIAGNOSTIC PROGRAMS — Diagnostic Programs for the central processor, memory and all peripheral equipment are provided. The central processor diagnostics execute the entire instruction repertoire in a wide variety of sequences while monitoring for errors. Programs for input/output channels and associated peripheral equipment test the ability of selected input/output units to generate or receive all acceptable data patterns in random and worst-case sequences.

APPLICATIONS PROGRAMMING — Systems Engineering Laboratories has developed a large number of applications programs for the SEL 810A including data acquisition, recording and logging, industrial process control, data display, data analysis, complex systems checkout and scientific computation. The resident programming staff is available to perform any programming tasks requested by the customer.

### **Customer Services**

FIELD MAINTENANCE — A skilled staff of customer engineers specializing in computer hardware operation, repair and programming is located at district offices in many major cities throughout the United States and Canada. These representatives offer SEL 810A customers immediate computer service and programming assistance. On call or resident service contracts are available.

DOCUMENTATION — Complete hardware and software documentation is available for the SEL 810A Computer. This includes computer and peripheral equipment maintenance manuals, program reference manuals, operation manuals and program maintenance manuals.

MAINTENANCE AND PROGRAMMING TRAINING — Maintenance and programming training courses are regularly scheduled at the Fort Lauderdale plant. Maintenance and programming training courses can also be conducted at the customers facility.

## Peripheral Equipment

CARD READERS/PUNCHES

| 81-450A | Reader |  | a. |  | 400 | cards/minute |

|---------|--------|--|----|--|-----|--------------|

| 81-440A | Punch  |  |    |  | 100 | cards/minute |

#### PAPER TAPE READERS/PUNCHES

| 81-510A Reader        |      | 300 characters/second |

|-----------------------|------|-----------------------|

| 81-520A Punch         | 4    | 110 characters/second |

| 81-525 Reader/Punch   | ÷    | 300/100 characters/   |

|                       |      | second                |

| 80-530A Paper Tape Sp | oole | er                    |

de deciri aper Tape opooler

#### MAGNETIC TAPE UNITS

- 81-610-78A Magnetic Tape Control Unit (7 Track) handles up to eight Magnetic Tape Units

- 81-610-98A Magnetic Tape Control Unit (9 Track) handles up to eight Magnetic Tape Units

- 80-615-09A Magnetic Tape Unit (7 Track) 75 ips - 200, 556 and 800 bpi

- 80-615-11A Magnetic Tape Unit (7 Track) 120 ips - 200, 556 and 800 bpi

- 80-615-12A Magnetic Tape Unit (7 Track) 150 ips - 200, 556 and 800 bpi

- 80-615-14A Nine track option for 80-615-07A, 09A, 11A and 12A 800 bpi

#### LINE PRINTERS

| 81-730A | 14 |  | 4 | 2 | 300   | lpm, | 120 | columns |  |

|---------|----|--|---|---|-------|------|-----|---------|--|

| 81-731A |    |  |   |   | 600   | lpm, | 120 | columns |  |

| 81-732A |    |  |   |   | 1,000 | lpm, | 120 | columns |  |

| 81-733A |    |  |   |   | 300   | lpm, | 120 | columns |  |

#### X-Y PLOTTERS

- 81-810A Incremental plotter, 12 inch chart width, 300 steps/sec.

- 81-812A Incremental plotter, 31 inch chart width, 200 steps/sec.

### GRAPHIC DISPLAY SYSTEM

80-816A 16 inch CRT display with vector generator, required magnetic deflection amplifiers and power supply

#### DISC FILE/CONTROL UNIT

| 81-653A |   |  |  | 1,024,000 word capacity |

|---------|---|--|--|-------------------------|

| 81-654A | × |  |  | Fixed Head Disc         |

|         |   |  |  | 227,000 word capacity   |

#### **TYPEWRITERS**

80-712A-ASR33, KSR33, RO33, ASR35, KSR35, RO35. . . 10 char/sec.

#### OTHERS

In addition to the full range of standard peripheral devices, a large variety of data acquisition, interface and control components are available with SEL 810A systems.

# **Basic SEL 810A**

### Specifications

WORD SIZE 16-bits plus parity bit and protect bit

INTERNAL MEMORY FULL CYCLE TIME 1.75 Microseconds

CORE STORAGE 4096 words directly addressable — expandable to 32,768 words

WORD TRANSFER RATE 572,000 words/second

COMPUTATION TIMES INCLUDING ACCESS AND INDEXING

| Add .    | 120 | <br>S415 |   |  | 3.5  | microseconds |

|----------|-----|----------|---|--|------|--------------|

| Subtract |     | 4        |   |  | 3.5  | microseconds |

| Multiply |     |          |   |  | 7.0  | microseconds |

| Divide . |     | <br>     | × |  | 10.5 | microseconds |

#### INPUT/OUTPUT UNIT

ASR33 Typewriter with Paper Tape Reader and Punch (10 characters per second)

#### ENVIRONMENT

Temperature (Storage) 0°F to 150°F Temperature (Operating) 50°F to 95°F Relative Humidity (Storage) 5 to 95% Relative Humidity (Operating) 30 to 90%

#### POWER

Power — 1,200 watts Voltage — 115 VAC ( $\pm$ 10%), 60 cps  $\pm$ 1% single phase

CIRCUIT BREAKERS Rating — 15 amp

#### WEIGHT 300 pounds

SIZE 23.25 inches wide 62 inches high 26 inches deep (41 inches including table top)

Bulletin 9032C

# Systems Engineering Laboratories

6901 West Sunrise Blvd., Ft. Lauderdale, Florida

District offices: San Francisco/Los Angeles/Chicago/ Cleveland/Orlando/Huntsville/Washington, D. C./ Boston/Houston/New York/Ottawa